服務熱線

0755-83044319

發布時間:2024-03-09作者來源:薩科微瀏覽:1865

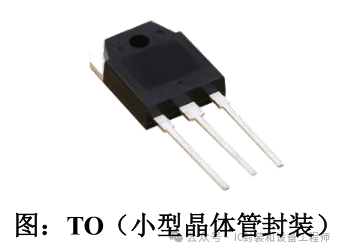

(1)20世紀50年代(小型晶體管封裝)

自1947年美國電報電話公司(AT&T)發明[敏感詞]只晶體管開始,半導體封裝也隨之出現。為了便于在電路上使用和焊接,封裝體要有外接引腳;為了固定微小的半導體晶粒,要有用于支撐的底座;為了保護晶粒不受大氣環境等的污染,也為了堅固耐用,就必須有把晶粒密封起來的外殼等。20 世紀50年代,首先出現了以三根引腳的TO(小型晶體管外殼)封裝。

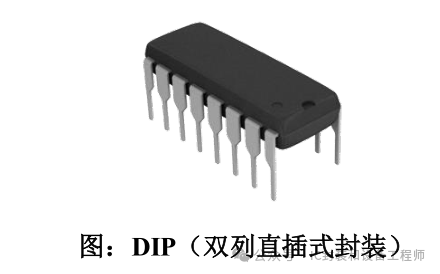

(2)20世紀60年代(雙列直插式封裝)

20世紀60年代中期,中小規模集成電路技術迅速發展,一塊集成電路晶粒往往集成了上千個晶體管或門電路,相應的其 I/O 數量也由數個發展到數十個,因此要求封裝外接引腳數量越來越多。在這種情況下,封測企業在 60年代開發出了 DIP(雙列直插式封裝)封裝形式。DIP 封裝形式有兩排引腳,需要[敏感詞]具有雙列直插式封裝結構的芯片插座上,其配套的PCB板需要進行穿孔工藝,DIP的引腳數一般[敏感詞]為64枚。

(3)20世紀70-80年代(扁平封裝)

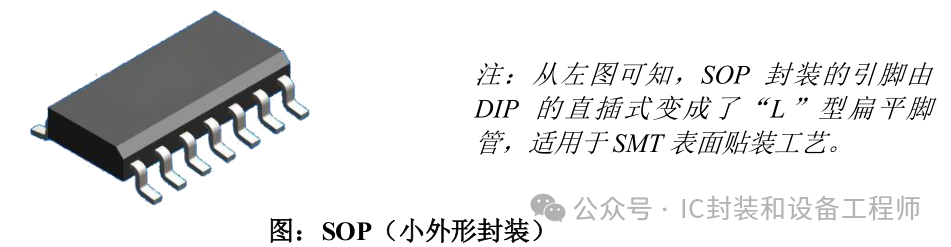

20世紀70年代隨著集成電路技術的不斷發展,中小規模集成電路逐步發展為大規模集成電路(Large Scale Integation,LSI),一枚晶粒上可集成上萬至數十萬個晶體管,這就對封裝體的引腳數量、I/O導出性能、電氣芯能、體積提出了更高的要求。此外,20世紀70-80年代表面貼裝技術(SMT)迅猛發展,同傳統PCB板穿孔組裝相比,扁平元器件貼裝面積大幅減少、自動化程度大幅提高,更適合大規模工業化生產。此外,貼裝元器件同PCB板的連接長度大幅縮短,降低了寄生電感和寄生電容的影響,提高了集成電路的高頻特性。

在行業需求推動下,20世紀70年代荷蘭飛利浦公司率先開發出[敏感詞]代適用于SMT工藝(表面貼裝工藝)的扁平封裝形式—SOP(小外形封裝)。SOP封裝實際為適于SMT工藝的DIP變型,其引腳數量和I/O導出芯能較DIP封裝提升不大。

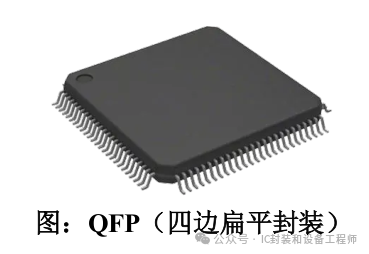

為了進一步在不大幅擴大封裝體所占面積的基礎上增加芯片的I/O數量,封裝企業在SOP封裝的基礎上,開發出了QFP(四邊扁平封裝)。QFP封裝引腳之間的間距很小,且腳管很細,引腳數目一般為44-208,甚至可以達到304之多,應用范圍較為廣泛。

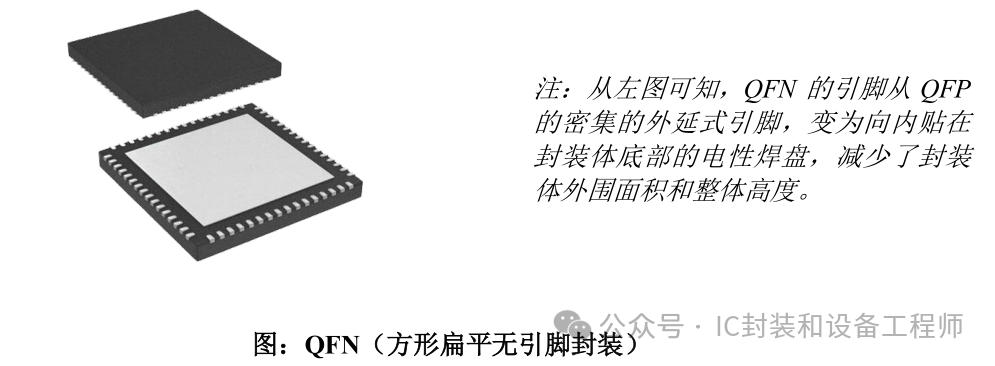

隨著集成電路終端應用設備向小型化發展,下游客戶對封裝后芯片的體積提出了更高的要求。由此,封裝企業在 QFP 的基礎上開發了 QFN 封裝形式(方形扁平無引腳封裝)。

QFN 封在封裝體底部四邊布有電極觸點,取消了向外延展的引腳,因此貼裝占有面積比 QFP 小,封裝體高度比 QFP 低。但受限于電極與電路板接觸面的應力影響,QFN 的電性焊盤數量無法達到 QFP 的引腳數水平。QFN 連接通路比 QFP 更短,擁有更好的電氣性能,且具備尺寸、散熱和成本優勢,因此終端應用場景非常廣泛,包括:藍牙芯片、WiFi 芯片、音頻芯片、電源管理芯片、功率放大芯片、基站時鐘芯片、視頻監控芯片等眾多領域。

目前 QFN 的發展趨勢為大尺寸、高集成,通過多芯片堆疊、高密度焊線、多層焊線、超密電性焊盤間距等技術,[敏感詞]增加 QFN 封裝的功能集成度I/O 數量,并在中性能芯片領域取代 QFP 和 BGA 封裝形式。在性能相仿的情況下,QFN封裝形式的價格較 BGA 至少低 30%、較 QFP 低 15%,因此芯片設計企業對高性能 QFN 封裝需求量較大。

態邏輯技術混合組件中首次使用了該項技術。但倒裝技術從 20 世紀 60 年代至 90 年代一直都未取得重大突破,直到 20 世紀 90 年代后隨著材料、設備及加工工藝的發展,同時隨著電子產品小型化、高速化、多功能趨勢的日益加強,倒裝技術再次得到集成電路封測行業的廣泛關注。

常規芯片封裝流程包括裝片、引線鍵合(焊線)兩個關鍵工序,而倒裝(FC,Flip Chip) 是通過晶圓凸點工藝(Bumping)在待封裝晶粒的電氣層表面形成一層呈陣列排布的金屬凸點(Bump),然后將金屬凸點直接與基板連接。

與常規焊線芯片相比,倒裝封裝工藝采用了凸點結構,互聯長度更短,互聯電阻、電感更小,封裝后芯片的電性能明顯提高。此外,由于倒裝工藝是將晶粒中的布線引出,再通過晶圓凸點工藝進行重新陣列排布,其 I/O 數量較焊線工藝大幅提升。

目前,倒裝技術作為先進封裝領域代表性技術之一,廣泛應用于從 QFN 到BGA 多種封裝形式之中。

②系統級封裝技術

隨著便攜式電子設備復雜性的增加,對集成電路芯片多功能、低功耗和輕薄性的要求越來越高,而使用先進晶圓制(10nm 及以下)將全部功能集成在一枚晶粒上的單芯片系統(SoC)面臨開發周期長、開發成本昂貴等問題。在這種情況下,系統級封裝技術應運而生。

系統級封裝并非專指一種技術,而是在工程設計基礎上,通過高精度裝片技術、高密度焊線技術、高精度 SMT 貼合技術、混合封裝技術、多種電磁屏蔽技術、多種底部填充技術等一系列先進技術,將多枚晶粒通過平鋪或堆疊的方式同電容、電阻、電感、天線等大量 SMT 元器件共同集成在一枚封裝體內的解決方案。通過系統級封裝,封測企業不僅將具備不同功能、使用不同材質的多枚集成電路晶粒集合在一起,同時還將原先獨立散落分布在 PCB 板上的大量SMT 元器件整合進封裝體內部。封裝體逐漸從芯片載體,發展為一塊系統模組,大幅提高了 PCB 板的空間利用率和組裝效率。

目前,系統級封裝產品已成為中高端先進封裝領域最常見的解決方案。

③晶圓級封裝技術

晶圓級封裝技術出現在 2000 年左右,是指在晶圓裸晶上進行部分或全部封裝加工。晶圓級封裝是晶圓凸點技術(Bumping)結合晶圓重布線(RDL,Redistribution layer)技術產生的一種封裝工藝,根據封裝結構的不同,可分為扇入式封裝(Fan-in)、扇出式封裝(Fan-out)等。

由于晶圓級封裝是在晶粒上進行封裝加工,因此其封裝體體積最小,在小型移動應用中具有較大優勢。此外,由于晶圓級封裝內部均使用晶圓凸點實現互聯,并通過晶圓重布線工藝進行了陣列排布,因此晶圓級封裝具有優異的電氣性能和 I/O 數量。

近年來,晶圓級封裝開發出通過硅通孔(TSV)互聯的多晶粒互聯、堆疊工藝,成為系統級封裝解決方案中重要技術工藝和發展方向。

免責聲明:本文采摘自網絡,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2025 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號