服務熱線

0755-83044319

發布時間:2025-07-10作者來源:薩科微瀏覽:697

作者 Simon Sabato為Cognichip公司聯合創始人兼首席架構師 | 前谷歌員工 | 前英特爾員工 | 前思科員工 | 前Cadence員工 | 方法論、架構、設計。

以下是他剛剛發表的一篇關于AI的文章:

一圖勝千言……真的是這樣嗎?

我在20世紀90年代于加州大學伯克利分校學習芯片設計,那是一個芯片通過“門級設計”(與門、或門等)組合在一起的時代。我是一個愛好者和書呆子,從我記事起就開始擺弄電池和燈泡。在上大學的至少六年前,我就已經開始使用隨處可見的“74xx”芯片構建電子設計,這些芯片在任何一家信譽良好的電子商店都能買到。當然,在大學里,事情變得更加嚴謹。我們學習如何將門電路組合在一起,以創建任意功能(如二進制加法器、交通信號燈控制器等),使用臭名昭著的“卡諾圖”。然后,我們學習如何優化這些設計,使用[敏感詞]批邏輯優化算法(比如伯克利分校自己的“Espresso”)。

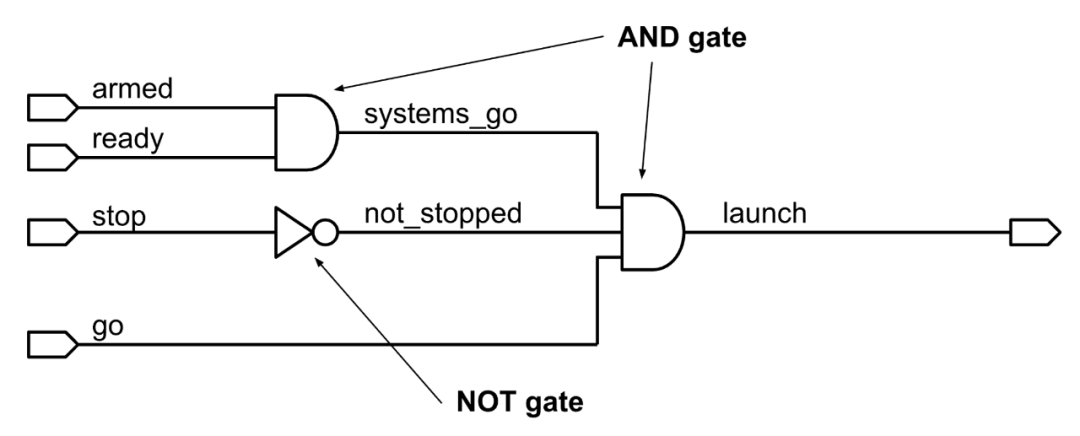

想象一個電路,當按下“開始”按鈕且我們沒有按下“停止”按鈕,并且處于“就緒”和“待命”狀態時,會產生一個“開始”信號。多年來,這種電路的門級設計是通過類似這樣的圖形用戶界面以原理圖的形式輸入的:

它看起來足夠簡單,但在得出上述設計之前,其實已經做出了一些選擇。我們可以將兩個與門合并以節省一些面積。我們也可以將“停止”信號進一步推到下游,作為靠近輸出端的“最終檢查”。然后,在我們決定采用上述電路設計之后,我們還需要從每個門的幾十種功耗/性能/面積變化中進行選擇。

為了做出所有這些選擇,“時序約束”被用來規定諸如“開始”導致“運行”之間允許的時間、處理“停止”信號的[敏感詞]時間,以及如果“停止”和“開始”信號幾乎同時接收時的預期行為等規則。

硬件描述語言(HDL)自20世紀80年代中期以來就已經存在,并且最近被納入了伯克利分校的課程體系。HDL是一種類似于普通編程語言(如C或Python)的書面語言,但它增加了邏輯設計所需的額外概念——并行計算、嚴格的事件時序以及對任意數據類型的支持。在我的[敏感詞]門計算機體系結構課程中,我們使用HDL來捕捉我們的門級設計——幾個門組合起來實現兩位數相加的電路被稱為“全加器”,然后32個這樣的全加器就構成了一個“32位加法器”,以此類推。

在選擇了每個門的確切變體后,用硬件描述語言(HDL)編寫的上述設計可能看起來像這樣:

module launch_control ( input armed, ready, stop, go, output launch ); wire systems_go, not_stopped; AND2_4X gate1 ( .IN1(armed), .IN1(ready), .OUT(systems_go) ); NOT_2X gate2 ( .IN(stop), .OUT(not_stopped) ); AND3_16X gate3 (.IN1(systems_go), .IN2(not_stopped), .IN3(go), .OUT(launch) );endmodule

用“代碼”來表達設計可以節省大量原本會花在圖形用戶界面中繪制導線上的時間(相信我,我兩種方式都試過!)。如果你覺得“我覺得看圖更容易理解”,你并沒有錯!只是代碼更容易編寫,而且維護起來更是難以估量地便捷。硬件描述語言(HDL)利用了為軟件代碼編寫的全部基礎設施——編輯器、版本控制系統、補丁格式等。在那門課程中,每個小型學生團隊都構建了一個32位RISC CPU內核:一個具有算術邏輯單元、寄存器文件和緩存的全流水線設計。

在20世紀90年代初,硬件描述語言(HDL)開始被用于測試設計。HDL具備像C這樣的軟件語言的所有功能:讀寫文件、生成隨機輸入、計算預期輸出等。除此之外,它們還增加了用于建模高度并行系統(如上述電路放大數百萬倍)所需的硬件特定功能。

HDL還被用于在更高層次上對硬件設計進行原型開發。大多數硬件模塊執行的算法相對簡單,只是執行速度非常快。通常很容易在高層次上編寫所需的函數。我們的火箭發射控制器可以被原型化為:

module launch_control ( input armed, ready, stop, go, output launch ); assign launch = (go && !stop && armed && ready);endmodule

這相當簡單!它沒有捕捉到具體的門電路組織和門類型的選擇,但它確實代表了最終版本將要做的事情。這在編寫測試用例、用原型化的部件構建并測試更大型系統等方面非常有用。與此同時,設計師會根據這種高層次的描述以及“時序約束”開始進行門級設計。通常,兩種版本都會被保留下來——高層次的代碼會運行得更快、更容易閱讀,也更容易調試……而門級設計才是你實際要構建的物理對象。

1994年:機器在芯片設計中擊敗人類?

我清楚地記得我[敏感詞]次聽到“綜合”這個詞的情景。在那門計算機體系結構課程快結束時,我和一位助教出去喝了一杯。我們討論了用代碼構建設計比用原理圖要方便得多,以及從“高級”代碼開始,然后在看到整個CPU工作之后再將其轉換為門電路是多么酷的一件事。他隨口提到:“你知道嗎,現在有一家公司開發了一種工具,可以自動將高級代碼轉換為門電路……他們叫Synopsys,他們把這叫作‘綜合’……它有個很無聊的名字,叫‘設計編譯器’……”

我的[敏感詞]反應是震驚,緊接著意識到這其實很有道理(“我怎么沒想到呢?這其實就是一個‘編譯器’……”)。下一個想法是,機器在將“高級”描述轉換為特定情境下的完美解決方案方面超越人類,肯定還需要很長時間。

在當時,大約是1994年,人們仍然主要靠手工編寫大多數對性能要求極高的軟件代碼,盡管高級語言和編譯器已經存在了幾十年。我以為芯片設計是最“性能敏感”的領域,所以也許我們會永遠在門級設計芯片!一般來說,硬件,尤其是芯片,建造成本極高——難道有人會為了節省一些工資而最終得到一個劣質產品嗎?

在酒吧的那次談話之后不久,我開始了我在3Com公司的[敏感詞]份全職工作,負責構建一款LAN+調制解調器接口卡。這項工作涉及設計一塊密布芯片的印刷電路板(PCB),以及設計一個現場可編程門陣列(“FPGA”)中的邏輯電路,以協調我們卡片的兩項功能。FPGA本質上是一種可編程芯片。它比“真正的”芯片更昂貴、速度更慢,但它是一種現成的部件,可以直接購買,而不需要花費大量的時間和金錢去制造定制芯片。在許多情況下,FPGA正是你所需要的。在3Com,我們的情況就是這樣——我們不需要太多的門電路,也不需要它們運行得很快。我們只需要一個交通警察,來引導流量通過一個三岔路口。

我知道我可以使用FPGA設計工具在圖形用戶界面中連接門電路,從而在門級完成這個設計。另一位設計師被分配來指導我。他來自走廊盡頭的ASIC團隊,他們最近剛剛完成了Etherlink III中的芯片設計,那是一款開始瘋狂暢銷的卡片……“互聯網泡沫”已經開始了。

那個產品中的ASIC是使用Synopsys設計編譯器構建的,這個名字讓我想起了什么。我的導師問我是否已經學過Verilog——“學校現在都在教這個,這是一種用代碼而不是繪制門電路來設計硬件的方法”——我回答說我用這種方法構建過一個32位CPU。“太好了,”他回答道,接著說“那你就不需要培訓了。”說完,他拿走了我最初精心繪制的幾張原理圖,開始用Verilog將它們“重寫”。代碼看起來完全陌生,但我太不好意思承認這一點了(又過了一年我才意識到,伯克利分校教的是VHDL,一種不同的語言)。

我仍然沒有被說服這個工具能設計得比我好,而且我不喜歡這種陌生的語言。我非常想放棄使用硬件描述語言(HDL)——我可以直接畫出門電路,然后就完成了。我的導師一直勸我不要這樣做;我記得有一次在掙扎的時候,我建議干脆放棄整個東西,花整個周末用原理圖重新繪制設計,我還記得他的話(“我不會希望任何人那樣做。我寧愿去打籃球”)。

隨著產品的演變,FPGA變得越來越復雜,空間也越來越緊張。高效設計變得越來越重要——也許我們對緊湊、高效設計的需求能讓我在這場與這個可惡的工具的較量中獲勝?!

我決定手工構建一個關鍵的狀態機。它只有幾十個門電路,但它必須運行得非常快,以便在罕見情況下捕捉到一個短暫的事件。它必須被放置在FPGA的一個小的、未被使用的角落里。我精心設計了我的電路。我的導師總是喜歡接受挑戰,他很快就回來展示了一個更好的版本。我沒有氣餒,進一步完善了我的設計,直到我確信不可能做得更好為止。然而,這個工具又找到了一個更好的解決方案。我開始懷疑綜合生成的版本可能無法正常工作,因為它生成了一些難以辨認的門電路。我浪費了寶貴的時間去檢查它,希望它犯了錯誤,結果卻發現它只是非常巧妙。盡管我對此表示欽佩,但另一個改進版本又出現了。我放棄了檢查它的成果,轉而繼續優化自己的設計。然而,又一個新版本出現了。

我放棄了,得出結論:“這玩意兒遲早會搶走我們的所有工作……”

這種想法,夾雜著一絲羞愧,在我的腦海中揮之不去。就好像我的同事有一根魔法棒,可以對設計編譯器說:“專注于讓這個設計更快……現在讓它更小……”,而它就像施展魔法一樣,飛速地篩選出數千種可能的解決方案。這感覺就像是他并不是在設計,而是在告訴它該設計什么。我怎么可能與之競爭呢??最終,我逐漸冷靜了下來。畢竟,當一個袖珍計算器比我乘法算得更快時,我也沒有自責過,不是嗎?你知道他們是怎么說的——如果你無法戰勝他們:那就全力以赴,轉到ASIC團隊,成為一名全職的Verilog編碼員。

有趣的是,Synopsys使用Verilog作為其工具的輸入語言。Verilog并不是為編譯成門電路而設計的,它可以表達許多綜合工具無法轉換成門電路的內容。我們最早學到的一件事就是語言的“可綜合子集”,這是一個不斷變化的邊界,并且包含一個相當大的灰色地帶(“它也許能做到,但你并不希望它做到”)。Verilog的表達能力意味著Synopsys(以及后來的其他公司)可以逐步擴展這個“可綜合子集”。Verilog逐漸演變為更強大的SystemVerilog,就像C語言演變為C++一樣。

總體而言,我認為綜合技術將生產力提高了大約1000%。讓我們來思考一下,在這段時間里芯片設計發生了多大的變化,以及事情變得多么復雜。

現代芯片可不是鬧著玩的

芯片設計團隊過去可能只有十幾個人,現在通常有大約一百人(范圍很廣——許多仍然由十幾個人的核心團隊完成,而有些則需要數百人)。過去,制造一塊芯片的成本是5萬美元,現在這個數字大約是2000萬美元。我設計的[敏感詞]塊FPGA有3000個門,我的[敏感詞]塊ASIC有5萬個門——相比之下,現代芯片的門電路數量達到了數十億。

我們應該把芯片視為一臺機器。這臺現代機器的齒輪被稱為“門”:

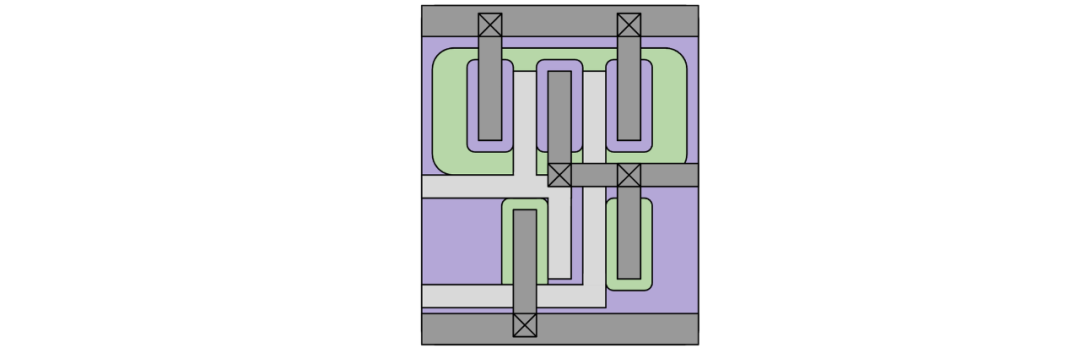

2輸入端與非門

上圖是一個簡單的門,包含四個晶體管。在紙上,導線看起來大約有5毫米寬,不同顏色代表不同的“層”——現代芯片大約有15層這樣的結構。

當我們說一款新手機配備了“5納米芯片”時,我們說的就是這些導線。這意味著我們的圖是按照1,000,000:1的比例繪制的(5毫米:5納米)。一塊典型的CPU芯片大約是12毫米×12毫米,按照這個比例繪制的話,它將是一個12公里×12公里的門電路陣列。

為了感受這些芯片處理數字的速度有多快,請考慮以下情況。在2025年,我們的手機通常有6個CPU核心,每個核心在2.5GHz的時鐘頻率下每秒執行約4條指令,這意味著它們每納秒可以處理60條指令。納秒是十億分之一秒,比光子以光速從手機傳播到我們臉部所需的時間還要短……芯片是一臺超高速的機器。

如今回看芯片設計,很難想象如果沒有邏輯綜合這一革命性技術,它們是如何被設計出來的。老實說,綜合確實取代了大部分涉及原理圖級設計的工作:它不僅做得更好、更快,還讓我們能夠專注于設計更大、功能更豐富的芯片。作為回報,它為我們帶來了如今蓬勃發展的半導體行業,該行業目前雇傭了33.8萬名員工,并且支持了300個下游經濟領域,為美國提供了超過2600萬個工作崗位[^SIA^]。

急需新的“綜合”時刻

盡管取得了令人印象深刻的增長和創新,半導體行業正面臨另一個轉折點。設計成本過高,且仍在上升。開發周期過長,且仍在增加。與此同時,就業市場數據預測,進入這一行業的工程師數量將出現巨大缺口。令人意外的是,芯片設計師的短缺問題比人工智能數據科學家更為令人擔憂。

人們已經多次嘗試尋找芯片設計生產力的下一個飛躍:

寄存器傳輸級(RTL)設計主要由SystemVerilog主導,但也有VHDL以及一些較小的“現代”語言,它們從根本上都處于“同一水平”——也就是說,編寫一個程序在它們之間進行轉換相對容易(與將RTL轉換為門電路不同)。

相比之下,高級綜合工具接受多種輸入語言(如C/C++、Python等),并將代碼“展開”,通常轉換為SystemVerilog。這種方法有其支持者和成功案例,但現實情況是,大多數主要芯片并不是這樣設計的。從根本上說,這種方法似乎能夠實現更快的設計周期,但代價是犧牲性能。在競爭激烈的市場中,我們通常不會選擇犧牲性能。

現在是時候在設計中邁向更高層次的抽象了,如果你愿意的話,可以稱之為新的“綜合”時刻。最近在人工智能領域取得的進步正在促使我們思考,自然語言是否可以成為我們的下一個“高級語言”。就像上次一樣,這將很快從同事隨意提及的事情,轉變為以令人難以置信的結果直面我們。

那么……人工智能會搶走我們的所有工作嗎?

回顧早期綜合工具的使用,我現在可以自信地回答:不會。

如果沒有綜合工具,確實我們需要更大的團隊來設計當今的芯片,但芯片市場的規模也會小得多——產品種類更少,成本更高,性能更低。大多數芯片設計工作將是單調、重復且薪酬較低的。一小部分人會負責高級設計工作,然后一大群人來完成剩下的工作——就像在好萊塢大片中,一群動畫師團隊負責“按部就班地填充顏色”。

芯片設計師會更愿意一直從事門級設計,而不是綜合出定義了21世紀的驚人芯片嗎?不,他們不會。

綜合工具推動了一個自1990年以來收入增長數倍的行業。出于類似的原因,我預計人工智能增強的芯片設計將增加工作崗位數量,并使工作更具吸引力。很快,將會有更多芯片被設計出來,每個芯片都更精準地針對其應用場景,具備更多功能,且成本更低、功耗更少。人工智能模型將使我們能夠構建更多我們想要的芯片,而不僅僅是那些我們能夠設計出來的芯片。

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2025 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號 ![]() 粵公網安備44030002007346號

粵公網安備44030002007346號